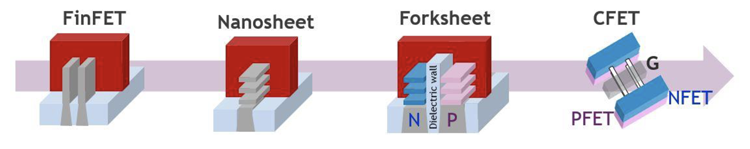

Компания TSMC подтвердила планы перехода на новые техпроцессы, транзисторы и технологии. В распространённом компанией документе чипы на 2-нм техпроцессе она начнёт выпускать в 2025 году и одновременно откажется от вертикально расположенных транзисторных каналов FinFET в пользу горизонтально расположенных каналов в виде наностраниц. О законе Мура на время придётся забыть, но энергоэффективность чипов существенно вырастет.

Источник изображения: TSMC

Также важным свойством наностраниц является более тонкая настройка транзисторов под задачи чипа, отсюда следует резко растущая энергоэффективность решений. Можно менять число страниц (каналов) и их ширину: для производительных чипов делать транзисторы с более широкими наностраницами, а для энергоэффективных — поуже.

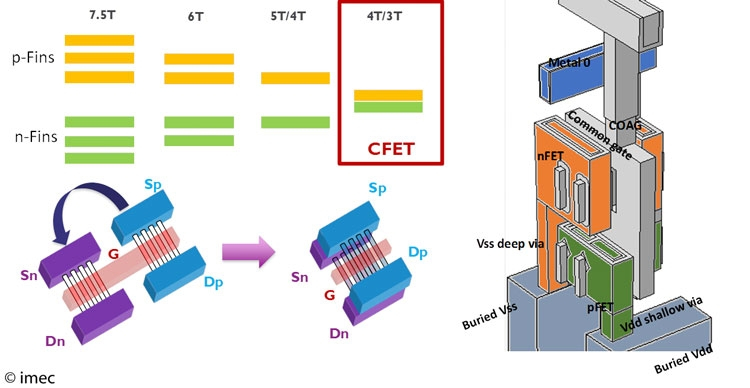

Интересно отметить, что TSMC также определилась, хотя это не окончательный выбор, со следующей конструкцией транзистора после 2-нм транзисторов с наностраницами. После наностраниц компания рассчитывает наладить производство чипов с транзисторами CFET (см. рисунок ниже). В своё время мы тоже рассказывали о таких. Одним из разработчиков транзисторов CFET или комплементарных FET является бельгийский центр Imec. Транзисторы CFET состоят из пары комплементарных полевых транзисторов n- и p-типа, но расположены они друг над другом, что позволяет, грубо говоря, в два раза увеличить плотность размещения транзисторов на кристалле.

Источник изображения: Imec

«Это [CFET] всё еще находится на стадии исследования, — сказал глава TSMC в интервью EE Times. — Это всего лишь один из вариантов транзистора. Я не думаю, что могу назвать сроки, когда эта транзисторная технология пойдет в производство».

Возвращаясь к 2-нм техпроцессу, отметим, что до его внедрения TSMC рассчитывает на долгую жизнь 3-нм техпроцесса с привычными транзисторами FinFET. Между этими техпроцессами будет не меньше трёх лет, но даже после начала производства 2-нм чипов компания рассчитывает долго продолжать выпуск 3-нм решений — они будут надёжными и проверенными временем.