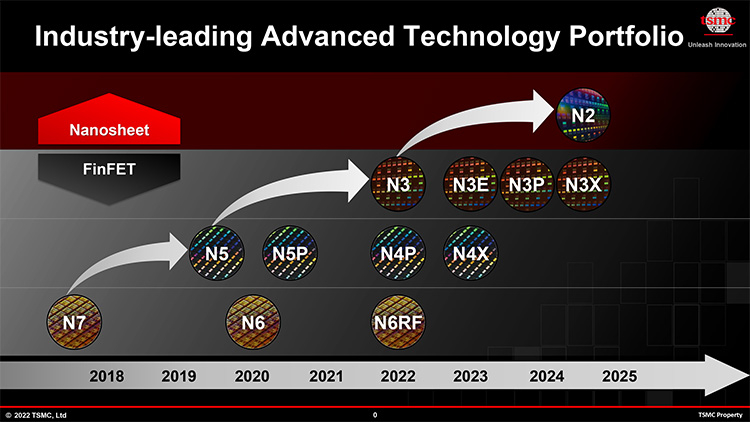

TSMC рассказала подробности о семействе техпроцессов N3 (3-нм класса), которые будут занимать место флагманских технологий полупроводниковой кузницы в период с начала 2023 по конец 2025 года. В семейство N3 в общей сложности войдёт пять техпроцессов разной специализации.

Технологический процесс N3E будет представлять собой усовершенствованную версию N3 с увеличенным выходом годных кристаллов. Достигаться это будет путём небольшого уменьшения разрешения литографии, за счёт чего плотность транзисторов на кристалле по сравнению с N3 откатится примерно на 10 %. Но зато снизится себестоимость чипов, и доступ к технологии 3-нм уровня получит широкий круг заказчиков. Более того, в целевых показателях техпроцесса N3E значится улучшение частотных и энергетических характеристик по сравнению с N3 на 3–4 %. Опытное производство чипов по технологии N3E запустится в третьем квартале текущего, а массовое производство — в середине следующего года. Таким образом поставки готовых N3E-изделий смогут начаться в конце 2023 года.

Техпроцессы N3P и N3S будут представлять собой варианты оптимизации N3E под различные классы применений. N3P ориентируется на высокопроизводительные чипы, а N3S — на энергоэффективные чипы с повышенной плотностью транзисторов. Оба техпроцесса запланированы на 2024 год.

Ещё один техпроцесс, N3X, появится в числе предложений TSMC ближе к 2025 году, когда компания начнёт осваивать следующую ступень полупроводниковых норм. Предназначение этой технологии — производство высокопроизводительных процессоров, для которых важно использование высоких рабочих токов и длительная работа на повышенных тактовых частотах.

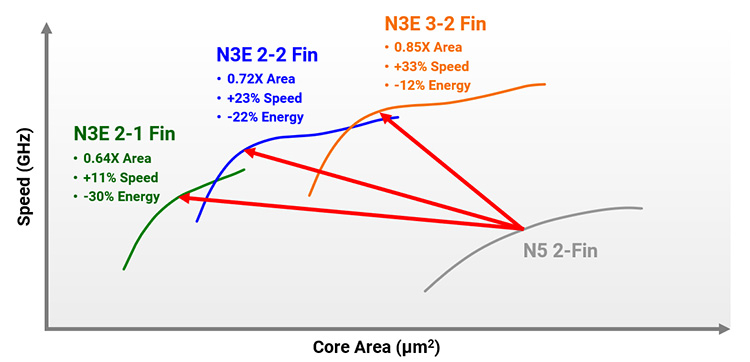

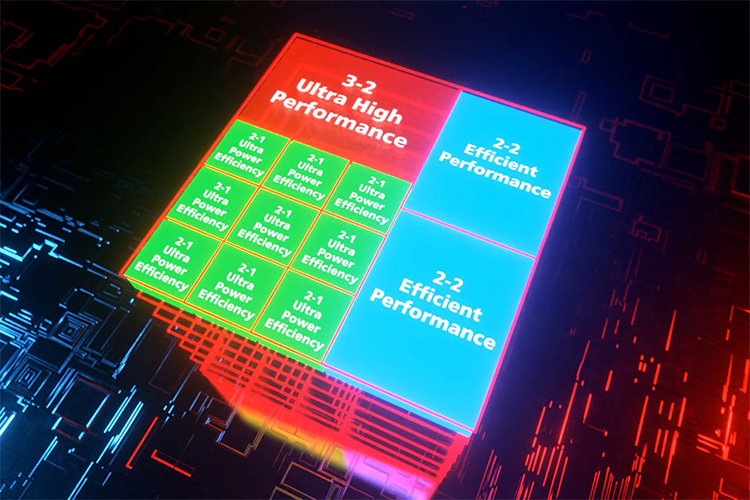

Говоря о процессах семейства N3, TSMC анонсировала технологию FinFlex, которая должна увеличить для заказчиков привлекательность чипов, выпускаемых компанией. Суть технологии состоит в том, что производитель позволит использовать библиотеки разных FinFET-транзисторов в рамках одного полупроводникового кристалла.

Набор доступных вариантов включает транзисторы с тройным затвором и двумя рёбрами канала (3-2 Fin), двумя затворами и двумя рёбрами (2-2 Fin) и двумя затворами и одним ребром (3-1 Fin). Первый тип транзисторов хорош для высокочастотных и высокопроизводительных применений, второй — для баланса между производительностью и энергоэффективностью, а третий — для энергоэффективных чипов с высокой плотностью. Разные транзисторы можно будет сочетать в рамках одного чипа, что позволит делать гибридные решения, в которых соседствуют производительные и энергоэффективные блоки. Технология FinFlex будет доступна для всего семейства техпроцессов N3.

Более тонкий, чем N3, техпроцесс TSMC намеревается ввести в строй в 2025-2026 году. В перспективной технологии N2 компания перейдёт на применение GAAFET-транзисторов и EUV-литографию с высоким числовым показателем апертуры.